應用場域與實例

我們的技術廣泛應用於半導體製程中各個階段。在上游,我們支持IC設計,提供靜電防護技術以確保設計過程中電子元件的安全性。在中游,我們專注於半導體設備零組件,我們的技術能在微小的電子元件上形成保護層,提高其抗靜電性能。至於下游,我們提供靜電防護解決方案給IC封測領域,包括封裝載具和治具,確保封裝過程中的電子元件不受靜電影響。無論在哪個製程階段,我們的技術都能提供全面的靜電防護,確保半導體製程中的穩定性和可靠性。

上游IC設計

中游IC製造

半導體設備零組件,鴻鎵的技術能在微小的電子元件上形成保護層,提高其抗靜電性能。

下游IC封測

鴻鎵提供靜電防護解決方案給IC封測領域,包括封裝載具和治具。

IC製造

在中游IC製造(半導體設備零組件)領域,我們最大的優勢在於技術的革新和可靠性。我們的技術能夠在半導體設備零組件上形成高效的靜電防護層,提高其抗靜電性能。透過我們的解決方案,能有效減少靜電對元件的損壞或干擾,確保製造過程中的穩定性和可靠性。我們不斷追求技術革新,致力於提供可靠且先進的靜電防護解決方案,使得半導體元件製造能夠更順暢、更可靠地進行。

IC 封裝/測試

我們提供封裝載具和治具的靜電防護解決方案。針對打線機等設備,我們的技術能有效保護並防止靜電對其運作和元件造成的潛在影響。我們的靜電防護技術廣泛應用於封裝過程中的各種治具和封裝載具,確保裝置運作的安全性和可靠性。透過我們的解決方案,能夠降低靜電對設備和元件的損害風險,提升封裝過程的穩定性,進而提高封測的品質和效率。我們的技術讓下游封測流程更穩定可靠,確保產品品質和生產效率。

實際應用

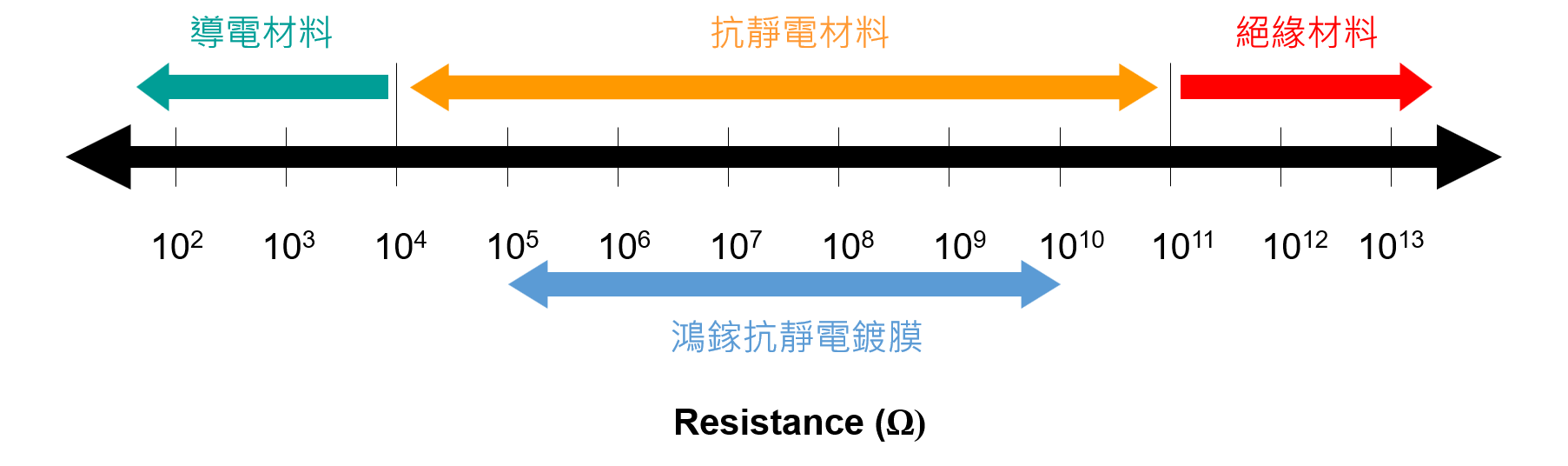

目前可達到1 x 105 ~1 x 109 Ω 的電阻值,我們的技術能提供靜電防護膜,這種膜能在特殊造型的工件表面形成,使其具有抗靜電能力。對於特殊造型工件也能透過我們的鍍膜技術,賦予其抗靜電膜,進而達到所需的電阻值。透過靜電防護膜的應用,能夠確保工件表面具有所需的電阻值,從而降低靜電對工件造成的損害或干擾,確保裝置的安全性和可靠性。

製程技術

先進鍍膜技術在導電範圍方面提供了廣泛的應用。這些技術可以在不同導電材料的表面形成具有抗靜電特性的薄膜或塗層,擴大了材料的導電範圍。

表面處理機制

-

抗靜電膜化性:在抗靜電表面處理過程中,抗靜電藥劑成分及製程影響膜之連續性,成膜越完整緻密、裂縫越少,表面阻抗越穩定,鴻鎵抗靜電藥劑能在寬廣的PH值範圍藉由特殊催化效果形成緻密且連續的抗靜電膜。

-

抗靜電膜物性:藉由調控抗靜電藥劑成分組成與厚度來決定表面電阻之大小。

先進鍍膜技術 4 大優勢

改善10奈米先進製程,提升良率

- 應用AI 人工智慧、電動車、低軌衛星 10 奈米以下技術。

- 在封裝過程中降低嚴重靜電效應。

- 可用於氮化鎵封裝製程良率提升。

耐磨耐高溫,無尺寸限制

- 不受尺寸限制,成本相較於現在抗靜電鍍膜技術有競爭力。

- 廣泛應用於半導體製程,包括製造、封裝和測試等環節。

國產技術,減少進口材料依賴

- 協助各相關企業單位在防靜電解決方案。

- 促進良率效能提升之全方位服務。

- 提升產業競爭力與銷售量。

高競爭力成本

- 改善目前抗靜電鍍膜製程繁瑣,不耐高溫,且有大尺寸限制。

- 提升成本競爭力及抗靜電壽命。

現有技術比較

PVD抗靜電技術及抗靜電塑料是國際競爭對手。PVD抗靜電技術提供優異的靜電防護,但在高溫環境下表現不佳。相較之下,抗靜電塑料在耐高溫方面表現優異,但成本高昂。鴻鎵科技的新技術擁有PVD抗靜電技術的靜電防護特性,並克服了高溫下的挑戰,同時提供更具競爭力的成本效益。這使得鴻鎵科技在提供高溫環境下靜電防護方面與國際競爭對手相比,具有更全面且具有競爭力的解決方案。

分析項目

$99.99

厚度

粗糙度(Ra)

緻密性

構型包覆性

附著性

表面電阻

靜電消散時間

耐溫

薄膜硬度(HV)

耐蝕能力

退鍍技術

鍍製價格

使用壽命

鴻鎵科技(國內)

$99.99

0.5-30 µm

< 3µm

優

優

優

可調控,均勻

適中

> 300°C

< 1500

優

可

低

長

SGS檢驗報告

SGS試驗報告中,測試產品中鋁合金板的表面阻抗檢測展現了鴻鎵卓越的抗靜電技術。檢測結果反映出鴻鎵產品優越的表面性能,符合國際標準,進一步彰顯鴻鎵公司抗靜電領域的競爭力。我們不僅擁有先進的技術,更致力於推動行業標準,為客戶提供高品質的產品。此報告的結果證明了我們在抗靜電技術方面的優勢,強化了客戶對我們品牌的信任。我們將持續不斷改進和創新,確保我們的產品在抗靜電性能方面保持領先地位,並繼續為客戶提供可靠的解決方案。