隨著全球AI運算需求噴發,半導體製程已進入極致微縮與高度整合的關鍵轉折點。從 NVIDIA H200到最新發表的GB200晶片,製程跨越5奈米、4奈米甚至直指2奈米,單顆晶片價值高昂,使得封裝端的「零失誤良率」成為晶圓大廠與系統商的最高目標。然而,製程越先進,對於「靜電放電」(ESD)的敏感度就越高。以 7 奈米手機晶片為例,封裝時頻發的靜電擊穿(Device Breakdown)一直是良率受損的主要痛點;而對於單價極高的 AI 晶片,任何細微的靜電損傷都意味著巨額損失。

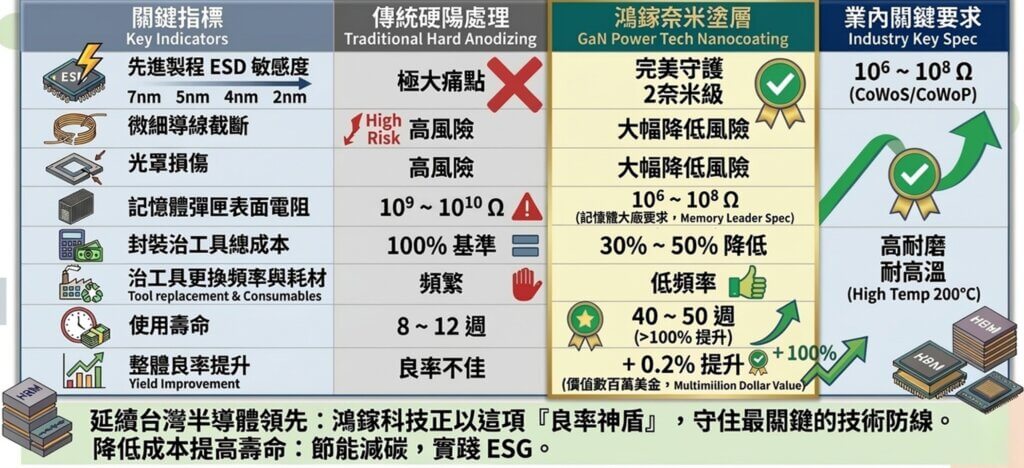

針對此嚴苛挑戰,鴻鎵科技宣布在「靜電控制表面處理」研發上取得突破性進展。業內消息指出,國際記憶體龍頭大廠已明確要求封裝彈匣(Magazine)的表面處理必須精準控制在106至108Ω之間,以確保記憶體晶片在封裝過程中的良率能趨近100%。此外,在當前最熱門的 CoWoS / CoWoP多層堆疊高附加價值晶片製程中,治工具對靜電控制的要求更為嚴格,必須穩定維持在106 至108Ω的範疇,方能承受多層堆疊過程中的精密操作。

鴻鎵科技研發出的特殊奈米塗層技術,正完美對接此市場需求。該技術不僅能提供穩定的表面靜電控制,更具備傳統硬陽處理所欠缺的高耐磨與耐高溫(200°C)性能。實測數據顯示,導入鴻鎵方案後,整體良率可提升約0.2%,對於追求極致良率的先進封裝產線而言,這0.2%即代表了數百萬美金的產值價值。

在經營效率上,鴻鎵技術同樣展現強大競爭力。透過延長治工具的使用週期,其鍍層壽命較一般處理提升 100% 以上(由 8-12 週大幅延長至 40-50 週),不僅顯著降低了耗材更換頻率,更協助半導體製造企業將治工具總成本降低 30%至50%。在追求效能與成本平衡的同時,亦助攻企業達成 ESG 永續管理目標。鴻鎵科技正以這項「良率神盾」,協助台灣半導體供應鏈在全球 AI 晶片競爭中,守住最關鍵的技術防線。